Soutenance de thèse 17/04/2023 - Paul Devoge - Développement de nouveaux dispositifs et étude des contraintes de conception « design » à leurs utilisations en technologies CMOS avancées pour les mémoires non volatiles embarquées

Soutenance de thèse Paul Devoge le Lundi 17 avril 2023 à 10h

Amphi Néel à Château-Gombert

Directeurs de thèse: Hassen Aziza (IM2NP) et Philippe Lorenzini (Université Côte d'Azur, Polytech’Lab)

Titre: Développement de nouveaux dispositifs et étude des contraintes de conception « design » à leurs utilisations en technologies CMOS avancées pour les mémoires non volatiles embarquées

Résumé

Alors que les coûts des usines et équipements de fabrication de semi-conducteurs augmentent d'année en année avec la complexification des technologies, certains acteurs de l'industrie tel que STMicroelectronics cherchent à se différencier non plus en jouant la course aux nanomètres et à la loi de Moore, mais en offrant des produits performants et généralement peu onéreux répondant à des besoins spécifiques, tels que les microcontrôleurs, les capteurs, les MEMS, l'électronique de puissance, etc.

Pour produire des circuits intégrés peu onéreux, il faut minimiser les coûts de fabrication, et c'est dans cette optique que les travaux de cette thèse se positionnent.

Les circuits intégrés doivent être fabriqués en utilisant le moins d'étapes de fabrication et de masques photolithographiques possibles.

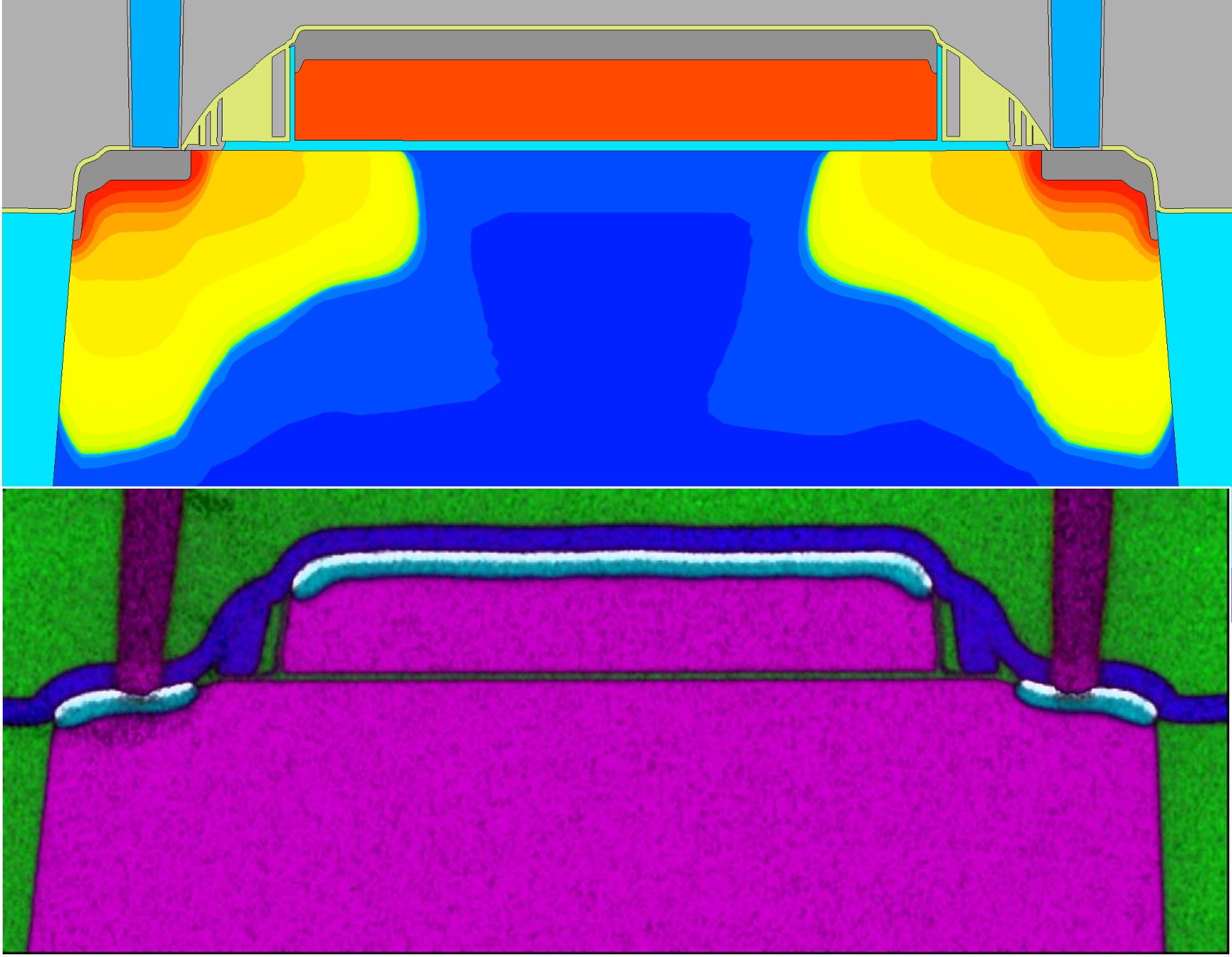

Dans cette thèse, plusieurs architectures de transistors à effet de champ à coût de fabrication ajouté nul sont proposées dans une technologie CMOS 34 nm embarquant une mémoire non volatile.

Ces architectures innovantes sont créées en réutilisant intelligemment des étapes de fabrication et masques déjà existants dans la technologie.

Les contraintes qui accompagnent l'utilisation d'architectures de transistor à coût nul sont étudiées du point de vue de la fabrication, de la performance électrique, de la fiabilité, et de la conception de circuits.

Ces transistors sont conçus sur ordinateur, leur comportement électrique est simulé, ils sont ensuite fabriqués et caractérisés en termes de performance et de fiabilité d'un point de vue du composant individuel jusqu'au circuits électroniques complexes.

Mots clés

transistor, MOSFET, CMOS, faible coût, fiabilité, procédé de fabrication, caractérisation électrique, moyenne tension, circuits intégrés, TCAD, analogique